芯片分析问答2025.7.1

- 2025-07-04 16:27:03

- 732

FA分析测DIE上的电容异常(怀疑静电损伤但未击穿),有什么好的方法吗?

A1

断开线路,单独把线路拉出来量测,如果有问题就做热点+FIB。

Q2

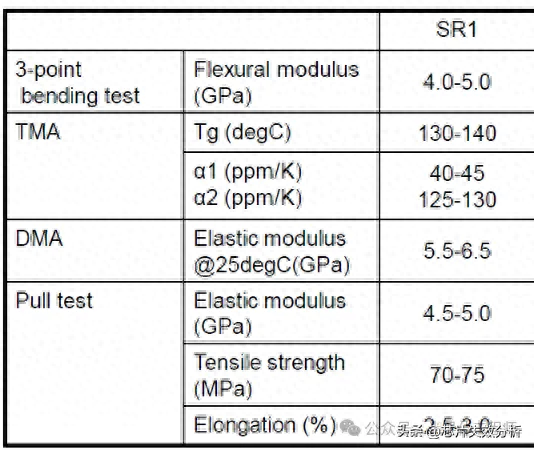

谁有AUSR1这个绿油的TDS吗,能帮忙分享一下吗?

A2

Q3

CP针痕扎在了pad边缘,这种会有品质风险吗?

A3

需要看铝墙形貌怎么样了,铝墙坏了打线容易出可靠性问题,一般铝墙没事情就没事,铝墙很容易看的,一般用显微镜看就行。

Q4

图中红框的位置发现疑似迁移,但是1这个铜条上了5V,2这个位置是0V,金属沉积的话应该是从左边开始才对,但是照片上貌似迁移是从右到左的,可以帮忙解释一下这个现象吗?

A4

看起來不那么像离子迁移、感觉更像烧伤或异物之类的,两种方法可以观察:1.把表面钝化层去除,再拍一次;2.直接FIB XS。

Q5

在进行BHAST老化板设计的时候,一些使能引脚OE需要拉高还是拉低?

A5

需要disable OE,就是不让IO输出,如果芯片自己drive high或者low,外面PCB上的上下拉就起不到作用了,OE一般是active low,所以一般上拉,disable OE。

Q6

BGA芯片在可靠性预处理reflow后部分芯片锡球氧化变色了,暗红色,这种属于正常现象吗?锡球表面打了成分也只有Sn,C,O。

A6

不正常。

Q7

测试有经验的帮忙评估下,Site一致性差异怎么评估,是否可接受?

A7

MSA或者GRR。

Q8

晶圆厂inline defect后段的报废标准比前段低的原因是什么?

A8

可能因为报废成本更高了,也有可能是认为关键制程已经稳定了,后续偏差的风险更低。

Q9

BHAST目的不就是为了验证吸湿后是否会因电离腐蚀引起电气失效吗?引脚出现发黑测试不通过,不就说明吸湿的电离腐蚀影响到了信号,为什么经过处理以后还可以认为考核是通过的?

A9

一般来讲BHAST管脚清洁处理不影响实验结果的,去除管脚沾污和氧化层,使用过程中管脚面是焊接上的,这部分不影响的。

Q10

Die在UV膜上的粘度有没有办法测?即芯片捡取的难易程度有没有办法量化?

A10

Die在膜上的附着力,TDS上有的,这个问题膜厂商应该可以回答。

Q11

车规IC产品必须要做的可靠性项目有哪些?是不是AEC-Q100里有些可靠性测试是不需要做的?

A11

测试群组A:环境压力加速测试,如室温、高温,湿度,温湿度循环等;

测试群组B:使用寿命模拟测试,室温、高低温寿命测试;

测试群组C:封装组装整合测试,主要是邦线相关的测试;

测试群组D:芯片晶圆可靠度测试,如电迁移,热载流子等;

测试群组E:电气特性确认测试;如ESD,EMC,短路闩锁等;

测试群组F:瑕疵筛选监控测试,过程平均测试及良率分析;

测试群组G:封装凹陷整合测试,包括机械冲击、震动、跌落等测试。

图片中上半部分的认证内容:

D组是在晶圆厂进行的验证内容,这部分内容偏重晶圆生产和工艺验证,一般会由Fab厂进行验证,没有自己晶圆生产能力的芯片公司Fabless不需要关注。

C组,是和封装工艺相关的验证内容,一般由封装厂进行验证,没有自己封装能力的芯片公司不需要关注,一般具备车规级晶圆和封测能力的代工厂,都具备16949认证和对应的AEC-Q验证能力,芯片公司要求对方提供相应的结果和报告就可以。

F组和E组的FG和CHAR内容,是晶圆厂和性能测试都需要关注的,属于通用标准,更像是统计方法的指导文件。

图片下半部分认证内容:A、B、E、G四组是功能、参数、电性能验证,这部分是芯片产品在封装后进行的验证内容,一般由芯片设计公司自行寻求第三方验证公司进行测试和报告的生成,这部分内容和产品性能、功能、应用强相关,也是芯片公司比较关注的重点,需要注意的是,E组同时出现在上下两个部分,但是包含的验证内容并不相同。

Q12

这是哪个计算寿命的加速模型吗?

A12

电容有时用这个模型,芯片很少用这个模型,这个是电压和温度加速组合模型,这个模型使用的前提是电压加速和温度加速因子相互独立、互不影响,这样两个加速因子才能直接相乘,类似用于温湿度加速的艾林模型,至于系数是否选3或2或10,你可以根据寿命测试数据去拟合,电压、电流和功率等经常用这种逆幂率模型,温度加速通常用阿伦尼斯或这种指数函数模型,你可以多选一些模型做拟合,看看那个拟合优度更高。

Q13

芯片封装后外箱进水,然后怎么处置,会不会影响可靠性?

A13

检测铝箔袋及湿度指示卡,铝箔袋不漏气,湿度卡没问题,觉得没什么问题,不放心过一道湿制程,再烘干重新包装。

Q14

ORT一般会安排做ELFR测试吗?

A14

如果高频次ORT做ELFR,有点费钱,一般是做HTOL,不做ELFR。

Q15

Scan测试有一定比例的IC需要在低于典型电压下才能pass,比如系统电源是0.9V,有些IC要在0.8甚至0.75V才能pass,大家有遇到过这种情况吗?

A15

数字后端没做好,可能setup time预留不够,也有可能是时钟出问题了,越低反而能pass,时钟路径没有约束好。

Q16

规范里为什么还要做高温存储?HTRB和HTGB不是应该可以覆盖它吗?

A16

覆盖不了的,失效机理不同的。

- 上一篇:三款机型无缘

- 下一篇:韩民众感叹泡面加蛋太奢侈